| Description | A2S56D20CTP is a 4-bank x 16,777,216-word x 4-bit, A2S56D30CTP is a 4-bank x 8,388,608-word x 8bit, A2S56D40CTP is a 4-bank x 4,194,304-word x 16bit double data rate synchronous DRAM , with SSTL_2 interface. All control and address signals are referenced to the rising edge of CLK. Input data is re... |

| Features |

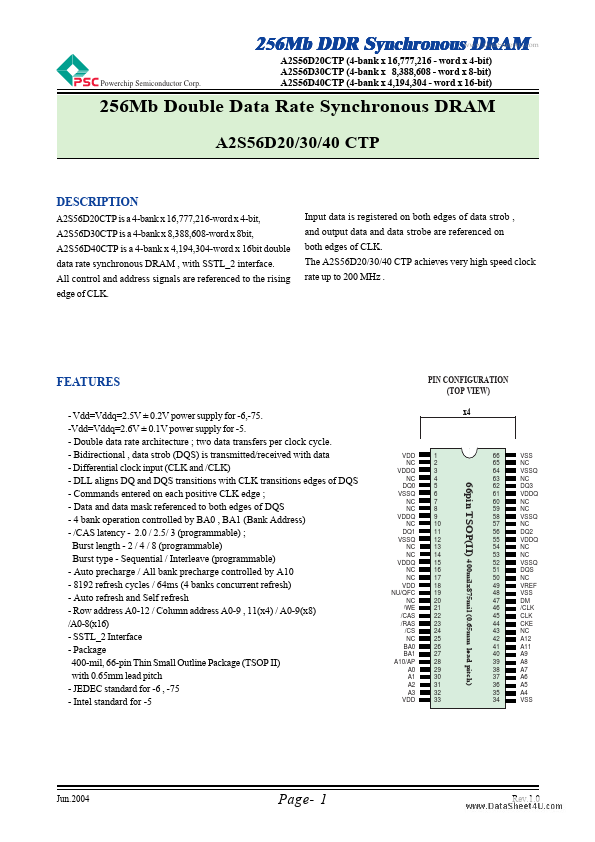

- Vdd=Vddq=2.5V ± 0.2V power supply for -6,-75. -Vdd=Vddq=2.6V ± 0.1V power supply for -5. - Double data rate architecture ; two data transfers per clock cycle. - Bidirectional , data strob (DQS) is transmitted/received with data - Differential clock input (CLK and /CLK) - DLL aligns DQ and DQS transitions with CLK transitions edges of DQS - Commands entered on each positive CLK edge ; - Data and data mask referenced to both edges of DQS - 4 bank operation controlled by BA0 , BA1 (Bank Address) - /CAS latency - 2.0 / 2.5/ 3 (programmable) ; Burst length - 2 / 4 / 8 (programmable) Burst type - ...

|

| Datasheet |

|

| Part Number | Description |

|---|