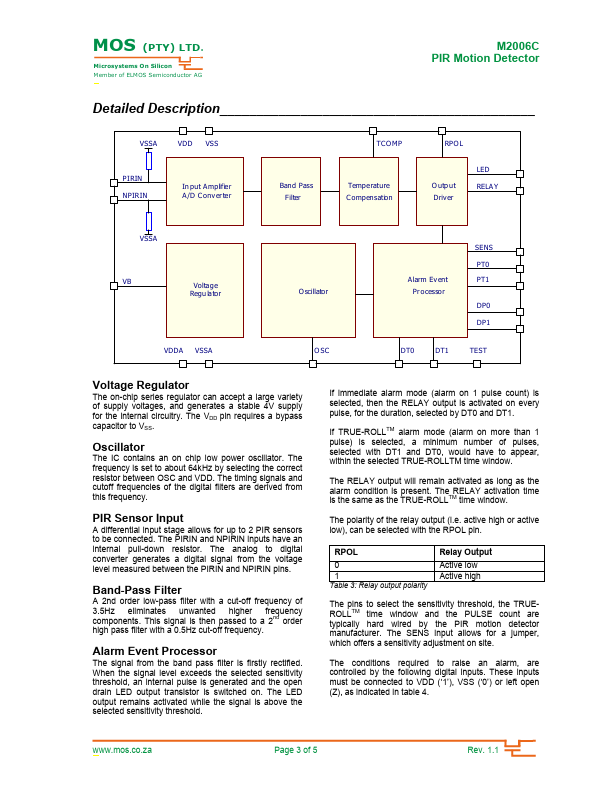

| Description | __________ The M2006C integrated circuit combines all required functions for a single chip Passive Infra Red (PIR) motion detector. A relay and a LED output are provided for interfacing to an occupancy detect or alarm system. One or two PIR sensors connect directly to the PIR inputs. The pull-down r... |

| Features |

____________________

♦ Digital signal processing ♦ On chip supply regulator with wide operating voltage range ♦ Low power consumption ♦ Temperature compensation input ♦ Differential PIR sensor input ♦ Selectable relay output polarity ♦ Selectable pulse count and timing algorithm for motion detection

Single Sensor Application Circuit________________________________

VSS

U1

14 VSSA VB 10

C1

D1

Supply

C2

11 12 VDDA PIRIN LED 20

L1

Alarm

R2 RE1

IRA1

RELAY 13 NPIRIN VDD

19

Alarm

2 1

T hre shold /Sensitivity PT0 5

PT1 4

OSC PT0 SENS PT1 RPOL

R1

N ear Far

VDD

3

S2

8 9 18 VSS

P uls...

|

| Datasheet |

|

| Part Number | Description |

|---|---|

MTRONPTI |

Clock Oscillator M2001 Series 5x7 mm, 3.3 Volt, CMOS/LVPECL/LVDS, Clock Oscillator • • Low cost oscillator series with jitter performance optimized specifically for Fibre Channel applications. CMOS, LVPECL, and LVDS versions available. Ideal for Fibre Channel, Storage Area Networks (SAN), and HDD Control www.DataSheet4U.com MtronPTI reserves the right to make changes to the product(s) and service(s) described herein without notice. No liability is assumed as a result of their use or application. Please see www.mtronpti.com for our complete offering and detailed datasheets. Contact us for your application specific requirements: MtronPTI 1-800-762-8800. Revision: 11-17-06 M2001 Series 5x7 mm, 3.3 Volt... |

Vishay Siliconix |

Ceramic/Cermet Attenuator M2001C Vishay Draloric Ceramic/Cermet Attenuator FEATURES • Symetrical T-Pad for control and/or reduction of signals on high frequency lines • Applicable for frequencies up to 1GHz • Matched to the characteristic impedance of coaxial antenna cable • Metal shielded • For vertical mounting • Applications: home cable TV, satelite TV, cable amplifiers, VHF/UHF output amplifiers STANDARD ELECTRICAL SPECIFICATIONS Resistive Element Wiper Contact Impedance Nominal Attenuation and Tolerance Insertion Loss up to 860MHz Reflexion Attenuation at 860MHz Adjustable Minimum Attenuation Operating Temperature Range Resistance to Soldering Heat Cermet, on ceramic substrate Metal 75R, (50R on special request) ... |

ICS |

Frequency Synthesizer The M2004-01 integrates a high performance Phase Locked Loop (PLL) with a Voltage Controlled SAW Oscillator (VCSO) to provide a low jitter Frequency Translator in a 9mm x 9mm surface mount package. The internal high “Q” SAW filter provides low jitter signal performance and determines the maximum output frequency of the VCSO. A programmable output divider can divide the VCSO frequency to achieve an output as low as 38.88MHz. FEATURES Output Clock Frequency up to 700MHz Differential LVPECL Outputs Internal Low-jitter SAW-based Oscillator Intrinsic Jitter <1ps rms (12kHz - 20MHz) Jitter Attenuation of Input Reference Clock Dual Input MUX Parallel Programming Tunable Loop Filter Response Diffe... |

ICS |

Frequency Synthesizer The M2004-02 integrates a high performance Phase Locked Loop (PLL) with a Voltage Controlled SAW Oscillator (VCSO) to provide a low jitter Frequency Synthesizer in a 9mm x 9mm surface mount package. The internal high “Q” SAW filter provides low jitter signal performance and determines the maximum output frequency of the VCSO. A programmable output divider can divide the VCSO frequency to achieve an output as low as 38.88MHz. The input to the Frequency Synthesizer is provided by selecting between a differential input clock or a single ended input clock. The output frequency is an integer multiple of the input reference frequency. The multiplying factor is programmed via a 6 bit parallel addr... |

Integrated Circuit Solution Inc |

VCSO BASED FEC CLOCK PLL / HITLESS SWITCHING OPTION The M2006-02 and -12 are VCSO (Voltage Controlled SAW Oscillator) based clock generator PLLs designed for clock frequency translation and jitter attenuation. They support both forward and inverse FEC (Forward Error Correction) clock multiplication ratios, which are pin-selected from pre-programming look-up tables. The M2006-12 adds Hitless Switching and Phase Build-out to enable SONET (GR-253) / SDH (G.813) MTIE and TDEV compliance during reference clock reselection. Hitless Switching (HS) engages when a 4ns or greater clock phase change is detected. This phase-change triggered implementation of HS is not recommended when using an unstable reference (more than 1ns jitter pk-to-pk) or when th... |

Integrated Circuit Solution Inc |

VCSO BASED FEC CLOCK PLL / HITLESS SWITCHING OPTION The M2006-02 and -12 are VCSO (Voltage Controlled SAW Oscillator) based clock generator PLLs designed for clock frequency translation and jitter attenuation. They support both forward and inverse FEC (Forward Error Correction) clock multiplication ratios, which are pin-selected from pre-programming look-up tables. The M2006-12 adds Hitless Switching and Phase Build-out to enable SONET (GR-253) / SDH (G.813) MTIE and TDEV compliance during reference clock reselection. Hitless Switching (HS) engages when a 4ns or greater clock phase change is detected. This phase-change triggered implementation of HS is not recommended when using an unstable reference (more than 1ns jitter pk-to-pk) or when th... |

Integrated Circuit Systems |

VCSO BASED FEC CLOCK PLL WITH HITLESS SWITCHING The M2006-12A is a VCSO (Voltage Controlled SAW Oscillator) based clock generator PLL designed for clock frequency translation and jitter attenuation. Clock multiplication ratios (including forward and inverse FEC) are pin-selected from pre-programming look-up tables. Includes Hitless Switching and Phase Build-out to enable SONET (GR-253) / SDH (G.813) MTIE and TDEV compliance during reference clock reselection. Hitless Switching (HS) engages when a 4ns or greater clock phase change is detected. This phase-change triggered implementation of HS is not recommended when using an unstable reference (more than 1ns jitter pk-to-pk) or when the resulting phase detector frequency is less than 5MHz. ... |

CHIMEI Innolux |

TFT LCD ...................................................................................................... 5 1.1 OVERVIEW ....................................................................................................................... 5 1.2 GENERAL SPECIFICATIONS ........................................................................................... 5 2. MECHANICAL SPECIFICATIONS .......................................................................................... 5 3. ABSOLUTE MAXIMUM RATINGS .......................................................................................... 6 3.1 ABSOLUTE RATINGS OF ENVIRONMENT................................................................ |

CHIMEI Innolux |

TFT LCD Global LCD Panel Exchange Center www.panelook.com 352'8&7 63(&,),&$7,21 'RF 1XPEHU ϭ 7HQWDWLYH 6SHFLILFDWLRQ ϭ 3UHOLPLQDU\ 6SHFLILFDWLRQ ɝ$SSURYDO 6SHFLILFDWLRQ 02'(/ 12 0 )*( 68)),; / &XVWRPHU &RPPRQ $33529(' %< 6,*1$785( 1DPH 7LWOH 1RWH 3URGXFW 9HUVLRQ & 3OHDVH UHWXUQ FRS\ IRU \RXU FRQILUPDWLRQ ZLWK \RXU $SSURYHG %\ ! ֆ࢙Ꮜ! ! ! &KHFNHG %\ ! ഋҥᒶ! ! ! 3UHSDUHG %\ ယӣ! 9HUVLRQ -XO\ 7KH FRS\ULJKW EHORQJV WR &+,0(, ,QQR/X[ $Q\ XQDXWKRUL]HG XVH LV SURKLELWHG One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory! www.panelook.com Global LCD Panel Exchange Center www.panelook.com 352'8&7 63(&,),&$7,21 &217(176 *(1(5$/ '(6&5,37,21 29(59,(: *(1... |

CHIMEI Innolux |

TFT LCD ...................................................................................................... 5 1.1 OVERVIEW ....................................................................................................................... 5 1.2 GENERAL SPECIFICATIONS ........................................................................................... 5 2. MECHANICAL SPECIFICATIONS .......................................................................................... 5 3. ABSOLUTE MAXIMUM RATINGS .......................................................................................... 6 3.1 ABSOLUTE RATINGS OF ENVIRONMENT................................................................ |

INNOLUX |

TFT LCD Module ......................................................................................................5 1.1 OVERVIEW........................................................................................................................5 1.2 GENERAL SPECIFICATIONS ..................................................................................... |

Chi Mei |

TFT LCD .................................................................................................................. 5 1.1 OVERVIEW 1.2 FEATURES 1.3 APPLICATION 1.4 GENERAL SPECIFICATIONS 1.5 MECHANICAL SPECIFICATIONS 2. ABSOLUTE MAXIMUM RATINGS ....................................................................................................... 6 2.1 ABSOLUTE RATINGS OF ENVIRONMENT 2.2 ELECTRICAL ABSOLUTE RATINGS 2.2.1 TFT LCD MODULE 2.2.2 BACKLIGHT UNIT 3. ELECTRICAL CHARACTERISTICS .................................................................................................... 8 3. 1.1 TFT LCD MODULE 3.1.2 Vcc Power Dip Condition 3.2 BACKLIGHT UNIT 4. BLOCK DIAGRAM .................. |

Chi Mei |

TFT LCD Module .................................................................................................................. 5 1.1 OVERVIEW 1.2 FEATURES 1.3 APPLICATION 1.4 GENERAL SPECIFICATIONS 1.5 MECHANICAL SPECIFICATIONS 2. ABSOLUTE MAXIMUM RATINGS ....................................................................................................... 6 2.1 ABSOLUTE RATINGS OF ENVIRONMENT 2.2 ELECTRICAL ABSOLUTE RATINGS 2.2.1 TFT LCD MODULE 2.2.2 BACKLIGHT UNIT 3. ELECTRICAL CHARACTERISTICS .................................................................................................... 8 3. 1.1 TFT LCD MODULE 3.1.2 Vcc Power Dip Condition 3.2 BACKLIGHT UNIT 4. BLOCK DIAGRAM ...................... |

Chi Mei |

TFT LCD Module .................................................................................................................. 5 1.1 OVERVIEW 1.2 FEATURES 1.3 APPLICATION 1.4 GENERAL SPECIFICATIONS 1.5 MECHANICAL SPECIFICATIONS 2. ABSOLUTE MAXIMUM RATINGS ....................................................................................................... 6 2.1 ABSOLUTE RATINGS OF ENVIRONMENT 2.2 ELECTRICAL ABSOLUTE RATINGS 2.2.1 TFT LCD MODULE 2.2.2 BACKLIGHT UNIT 3. ELECTRICAL CHARACTERISTICS .................................................................................................... 8 3. 1.1 TFT LCD MODULE 3.1.2 Vcc Power Dip Condition 3.2 BACKLIGHT UNIT 4. BLOCK DIAGRAM ...................... |

Chi Mei |

TFT LCD Module .................................................................................................................. 5 1.1 OVERVIEW 1.2 FEATURES 1.3 APPLICATION 1.4 GENERAL SPECIFICATIONS 1.5 MECHANICAL SPECIFICATIONS 2. ABSOLUTE MAXIMUM RATINGS ....................................................................................................... 6 2.1 ABSOLUTE RATINGS OF ENVIRONMENT 2.2 ELECTRICAL ABSOLUTE RATINGS 2.2.1 TFT LCD MODULE 2.2.2 BACKLIGHT UNIT 3. ELECTRICAL CHARACTERISTICS .................................................................................................... 8 3. 1.1 TFT LCD MODULE 3.1.2 Vcc Power Dip Condition 3.2 BACKLIGHT UNIT 4. BLOCK DIAGRAM ...................... |

Chi Mei |

TFT LCD Module .................................................................................................................. 5 1.1 OVERVIEW 1.2 FEATURES 1.3 APPLICATION 1.4 GENERAL SPECIFICATIONS 1.5 MECHANICAL SPECIFICATIONS 2. ABSOLUTE MAXIMUM RATINGS ....................................................................................................... 6 2.1 ABSOLUTE RATINGS OF ENVIRONMENT 2.2 ELECTRICAL ABSOLUTE RATINGS 2.2.1 TFT LCD MODULE 2.2.2 BACKLIGHT UNIT 3. ELECTRICAL CHARACTERISTICS .................................................................................................... 8 3.1 TFT LCD MODULE 3.1.1 Vcc Power Dip Condition 3.2 BACKLIGHT UNIT 4. BLOCK DIAGRAM ......................... |